# **Experiment: LOGIC GATES**

Object: To verify the truth table of basic gate (NOT, AND, OR) and universal gates (NAND and NOR) using RTL (using Resistor Transistor Logic)/ DTL (Diode Transistor Logic) circuits.

Apparatus used: Resistor, diode, transistor, LED, 5-volt power supply, IC and connecting wires.

#### Formula and circuit diagram:

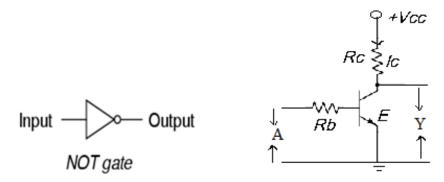

[1] NOT Gate :  $Y = \overline{A}$

Figure 1: RTL as NOT gate

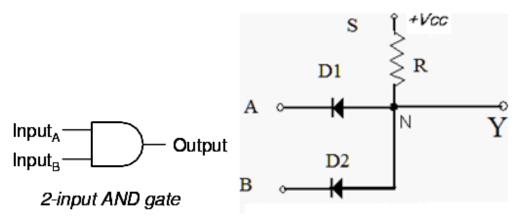

[2] AND Gate: Y= A.B

Figure 2: Diode circuit as AND gate

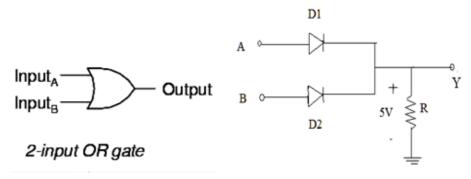

[3] OR Gate: Y= A + B

Figure 3: Diode circuit as OR gate

# **Experiment: LOGIC GATES**

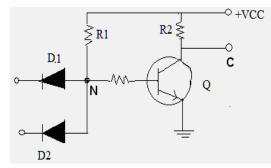

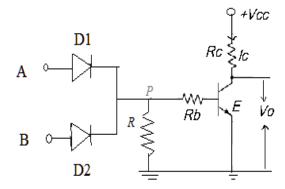

#### [4] NAND Gate: $Y = \overline{A.B}$

2-input NAND gate

Equivalent gate circuit

Figure 4: DTL as NAND Gate

# [5] NOR Gate: $Y = \overline{A + B}$

$$\frac{\mathsf{Input}_{\mathsf{A}}}{\mathsf{Input}_{\mathsf{B}}}$$

Output  $=\frac{\mathsf{Input}_{\mathsf{A}}}{\mathsf{Input}_{\mathsf{B}}}$  Output

# 2-input NOR gate

# Equivalent gate circuit

Figure 5: DTL as NOR Gate

# Observation:

# 1. Truth Table for NOT gate

| Α | $\overline{A}$ |

|---|----------------|

| 0 | 1              |

| 1 | 0              |

# **Experiment: LOGIC GATES**

#### 2. Truth Table for AND gate

| Α | В | A.B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

#### 3. Truth Table for OR gate

| Α | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

# 4. Truth Table for NAND gate

| Α | В | A.B | $Y = \overline{A.B}$ |

|---|---|-----|----------------------|

| 0 | 0 | 0   | 1                    |

| 0 | 1 | 0   | 1                    |

| 1 | 0 | 0   | 1                    |

| 1 | 1 | 1   | 0                    |

#### 5. Truth Table for NOR gate

| Α | В | A+B | $Y = \overline{A + B}$ |

|---|---|-----|------------------------|

| 0 | 0 | 0   | 1                      |

| 0 | 1 | 1   | 0                      |

| 1 | 0 | 1   | 0                      |

| 1 | 1 | 1   | 0                      |

RESULT: The truth table for basic logic gates are verified.

#### Precaution:

- 1. Input must be off 5 volts.

- Connections should be jointed correctly.

Connections must be tight.